Towards reliable high-temperature stable SiC CMOS technology - concepts, challenges and solutions (HT CMOS)

Internally funded project

Acronym: HT CMOS

Start date : 01.09.2021

Project details

Short description

This work aims to enable a high-temperature stable 4H-SiC technology to fabricate CMOS devices.

Scientific Abstract

Addressing temperature ranges between room temperature and 500 °C places multiple challenges on the devices and thus the technology used to fabricate them. As these have yet to be completely solved, several points must be optimized from its current state.

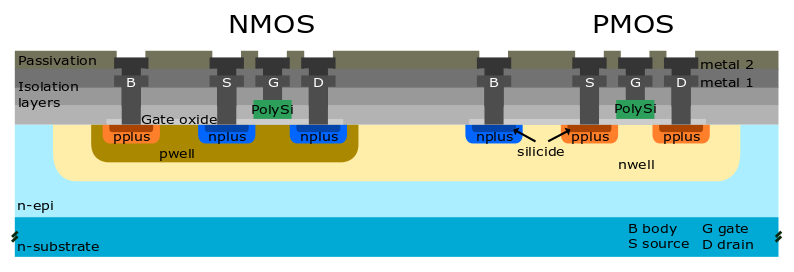

The electrical contact between SiC and the metallization must be optimized to behave ohmic within the whole temperature range for both NMOS and PMOS. Therefore, the size of the contact vias also become relevant, as well as the contact materials and the silicidation process. Metallization and passivation layers must withstand the harsh environment, including the high temperature. Ideally, a second metal layer must be available to provide routing options for more complex integrated circuits. Also, the technology must be adjustable within certain degree depending on special requirements of customers and applications without impacting its reliability. One such example could be threshold voltage adjustment. All these points need to be solved to contribute this technology platform for further scientific research. With it, it would be possible to fabricate different sensor types, including on-chip readout electronics, which can for example be used in gas turbines or aircraft and rocket engines to monitor multiple parameters.

This work aims to enable a high-temperature stable 4H-SiC technology to fabricate CMOS devices. To accomplish this, existing process modules will be extended, and novel ones created. These will be modularly integrate able into the process flow. Fabricated process control structures and single transistors will be characterized to extract material and device characteristics and to further optimize them.