HYPNOS – Co-Design of Persistent, Energy-efficient and High-speed Embedded Processor Systems with Hybrid Volatility Memory Organisation (HYPNOS)

Third Party Funds Group - Sub project

Acronym: HYPNOS

Start date : 21.09.2022

End date : 21.09.2025

Website: https://spp2377.uos.de/

Overall project details

Overall project

DFG-Schwerpunktprogramm (SPP) 2377 - Disruptive Speichertechnologien

Project details

Short description

Short description

This project is funded by the German Research Foundation (DFG) within the Priority Program SPP 2377 "Scalable Data Management for Future Hardware".

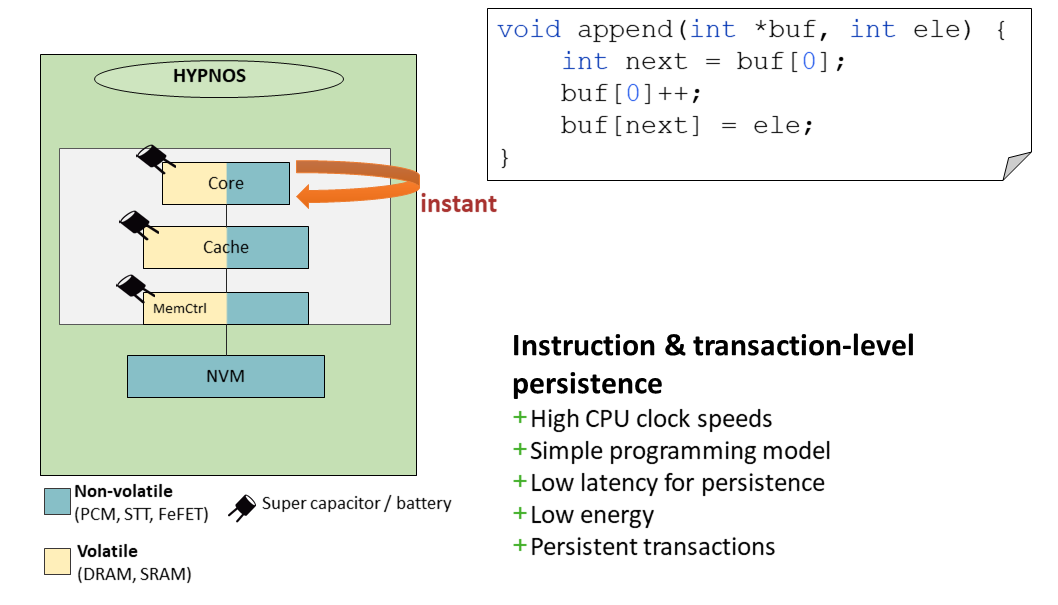

HYPNOS explores how emerging non-volatile memory (NVM) technologies could beneficially replace not only main memory in modern embedded processor architectures, but potentially also one or multiple levels of the cache hierarchy or even the registers and how to optimize such a hybrid-volatile memory hierarchy for offering high speed and low energy tradeoffs for a multitude of application programs while providing persistence of data structures and processing state in a simple and efficient way.

On the one hand, completely non-volatile (memory) processors (NVPs) that have emerged for IoT devices are known to suffer from low write times of current NVM technologies as well as by orders of magnitude lower endurance than, e.g., SRAM, thus prohibiting an operation at GHz speeds. On the other hand, existing NVM main memory computer solutions suffer from the need of the programmer to explicitly persist data structures through the cache hierarchy.

HYPNOS (Named after the Greek god of sleep.) systematically attacks this intertwined performance/endurance/programmability gap by taking a hardware/software co-design approach:

Our investigations include techniques for

a) design space exploration of hybrid NVM memory processor architectures} wrt. speed and energy consumption including hybrid (mixed volatile) register and cache-level designs,

b) offering instruction-level persistence for (non-transactional) programs in case of, e.g., instantaneous power failures through low-cost and low-latency control unit (hardware) design of checkpointing and recovery functions, and additionally providing

c) application-programmer (software) persistence control on a multi-core HyPNOS system for user-defined checkpointing and recovery from these and other errors or access conflicts backed by size-limited hardware transactional memory (HTM).

d) The explored processor architecture designs and different types of NVM technologies will be systematically evaluated for achievable speed and energy gains, and for testing co-designed backup and recovery mechanisms, e.g., wakeup latencies, etc., using a gem5-based multi-core simulation platform and using ARM processors with HTM instruction extensions.

As benchmarks, i) simple data structures, ii) sensor (peripheral device) I/O and finally iii) transactional database applications shall be investigated and evaluated.

Scientific Abstract

Dieses Projekt wird durch die Deutsche Forschungsgemeinschaft (DFG) im Rahmen des Schwerpunktprogramms SPP 2377 "Disruptive Memory Technologies" gefördert.

HYPNOS untersucht den Einsatz emergenter nichtflüchtiger Speichertechnologien (engl. NVM) nicht nur im Bereich des Hauptspeichers, sondern auch über die gesamte Cache-Hierarchie und Register moderner eingebetteter Prozessoren hinweg. Insbesondere wird untersucht, welche Vorteile eine solche gemischt volatile Speicherhierarchie hinsichtlich hoher Taktraten und niedrigem Energieverbrauch für eine Vielzahl von Anwendungen bringt und dabei gleichzeitig Persistenz von Datenstrukturen und Prozessorzustand einfach und effizient zusichert.

Zum einen können emergente Prozessoren aus dem IoT-Bereich mit vollständig nichtflüchtigen Speichern (sog. NVPs) nur mit relativ geringen Taktraten betrieben werden aufgrund deutlich höherer Schreibzeiten für NVM-Speicher als auch um Größenordnung geringerer sog. Endurance als z.B. SRAM. Taktraten im Bereich von GHz sind daher nicht möglich. Zum anderen fordern existierende Rechner mit NVM-Hauptspeichererweiterungen dem Programmierer ab, Datenstrukturen explizit durch die Speicherhierarchie durch Spezialbefehle zu persistieren.

HYPNOS (benannt nach dem griechischen Gott des Schlafes) attackiert den Konflikt zwischen Performance, Endurance und Programmierbarkeit systematisch basierend auf einem Hardware/Software Co-Design-Ansatz:

Unsere Untersuchungen umfassen

a) Entwurfsraumexploration von Prozessoren mit hybrid-volatiler Speicherarchitektur hinsichtlich Performance und Energieverbrauch.

b) Zusicherung von Persistenz auf Instruktionsebene für (nicht-transaktionale) Programme; während Phasen von Spannungsausfällen durch effizientes und kostengünstiges Checkpointing und Recovery in Hardware abgefangen werden.

c) Programm-gesteuerter Persistenzkontrolle durch den Anwendungsprogrammierer (Software) für Mehrkern-HYPNOS-Prozessoren zur Implementierung anwendungsspezifischer Checkpointing- und Recovery-Mechanismen für diese und andere Fehlerszenarien oder Zugriffskonflikten unterstützt durch einen größenbegrenzten Hardware-Transaktionsspeicher (HTM).

d) Die explorierten Prozessorarchitekturvarianten und verschiedene Typen emergenter NVM-Technologien sollen systematisch evaluiert werden bzgl. erreichbarer Taktraten und Energieeinsparungen und zum Test der HW/SW Backup- und Recovery-Mechanismen hinsichtlich Recovery-Latenzen, etc., unter Nutzung einer gem5-basierten Simulationsplattform für Mehrkernprozessoren. Speziell sollen Erweiterungen von ARM-Prozessoren mit HTM-Instruktionssatzerweiterungen untersucht werden.

Als Benchmark-Anwendungen sollen i) einfache Datenstrukturen, ii) Sensor-spezifische I/O-Funktionen und letztendlich iii) Datenbanktransaktionen gemeinsam evaluiert werden.